研究開発活動

研究開発体制

当社は「環境にやさしい低コスト工法の開発」をテーマに、コストの削減、ひいては世界のデファクト・スタンダード実現に向けて積極的な研究開発活動をおこなっています。当社の研究開発活動は大きく分けて

- 現在の市場から求められている新製品や技術に対応した製品の開発

- 直近から数年先に実現が予想されるプリント基板の新しい技術と実用化に向けて新技術の開発

- プリント基板の要素技術、次世代基板、特殊基板

からなります。そのほか、各生産拠点における量産技術、品質・信頼性向上技術、省エネ技術、環境技術等について、最も適切な技術を開発し、全拠点へ展開していくことも含まれます。

以下にこれらの具体的開発テーマについて紹介します。

部品内蔵基板 M-VIA Embedded®

モバイル機器の更なる高性能・小型化に向けて狭ピッチ電極ベアチップや小型受動部品の部品内蔵技術に取り組んでいます。また、近年は自動車パワーIC内蔵の必要性も増えていることから、大電流・高放熱を実現する部品内蔵技術やシミュレーション技術にも積極的に取り組んでいます。

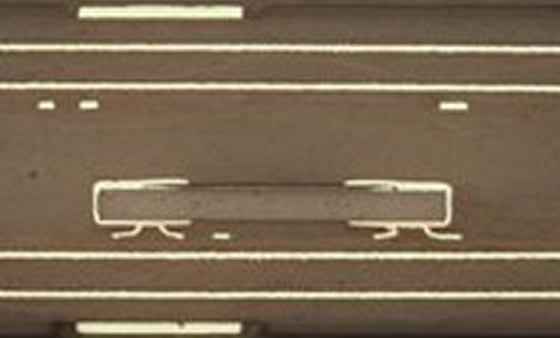

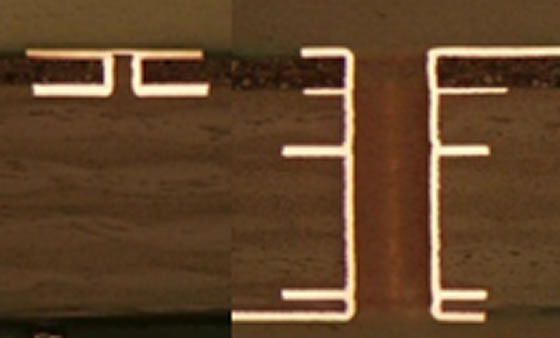

超厚銅基板

配線層の銅厚をより厚く、多層構造にすることで大電流を流すことができる超厚銅基板の開発に取組んでいます。配線層厚アップや同一樹脂による一体成形に取組み、大電流対応と高信頼性を両立した基板形成技術の開発を進めています。

高周波ハイブリッド基板

様々な高周波材料(PTFE・LCP・PPE・Low-k Epoxy)と一般材料(FR-4)をハイブリッド構造にすることにより、高周波回路と制御回路の一体化による基板の薄型・小型化を実現します。更に高密度配線に向けてマイクロビア形成や高周波材料の多層化にも取り組んでいます。また、新たな高周波材料に対して、材料特性や伝送特性などの評価を社内で行います。

0.3mmピッチCSP搭載基板(M-VIA Any™)

スマートフォンを代表とするモバイル機器の小型・軽量・多機能化に向けて、0.35mmピッチCSP及び0.3mmピッチCSP が今後の主流となることが予想されます。当社は、これらの配線に対応する全層ビルドアップ構造、レーザービア小径化、ビアランド小径化、狭ピッチ回路形成技術の開発に取り組んでいます。

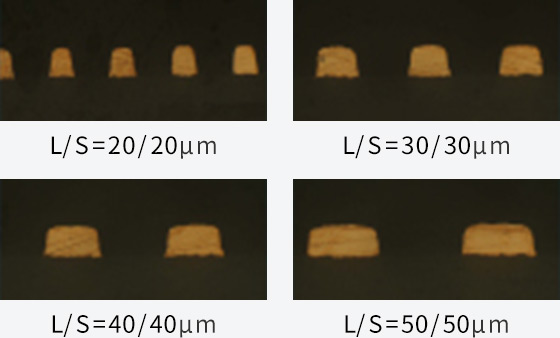

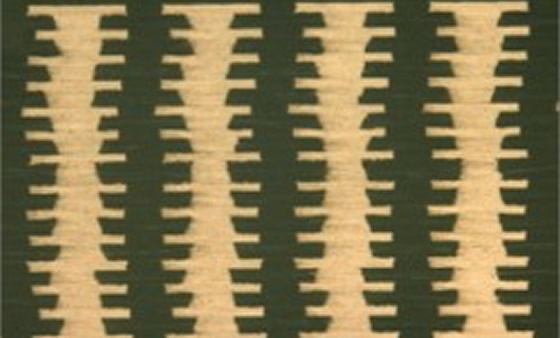

セミアディティブビルドアップ基板

CSPの更なる狭ピッチおよび多ピン化に向けて、CSP電極間の配線本数を現行の1本から2本以上とし、配線容量の増加を図る必要が有ります。そのためにはL/S=40/40μm以下の微細配線形成技術が必要となるため、従来のエッチング工法に代わる、銅箔ベースのセミアディティブ工法の開発に取り組んでいます。